技術紹介

TECH EXTENSIONは

東京科学大学 科学技術創成研究院 大場隆之研究室の成果を活用します。

技術の詳細については、大場研究室のサイトもあわせてご覧ください。 [リンク]

我々のブレークスルー : BBCube

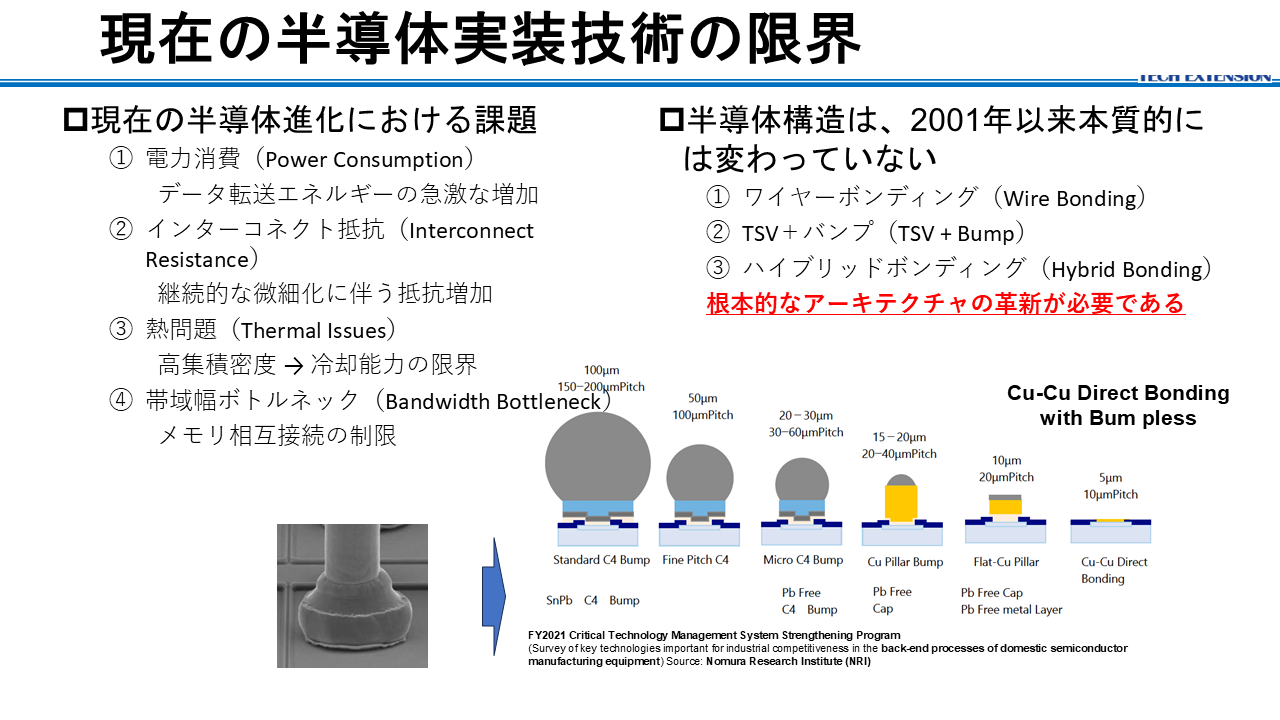

BBCube(Bumpless Build Cube)は、半導体の未来を拓く次世代3次元アーキテクチャです。

東京工業大学「WOWアライアンス」の英知によって開発されたこの革新技術は、Wafer-on-Wafer(WOW)とChip-on-Wafer(COW)を高度に統合させています。

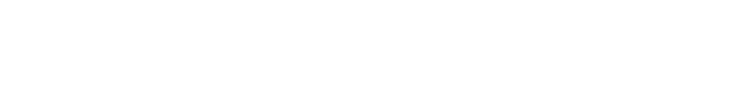

超薄型ウェハーと高密度TSVインターコネクトを採用した究極の積層構造により、ミクロンレベルのデバイス近接配置という異次元の性能を実現可能にします。

この技術が、従来の構造的制約を打ち破る真のブレークスルーとなります。

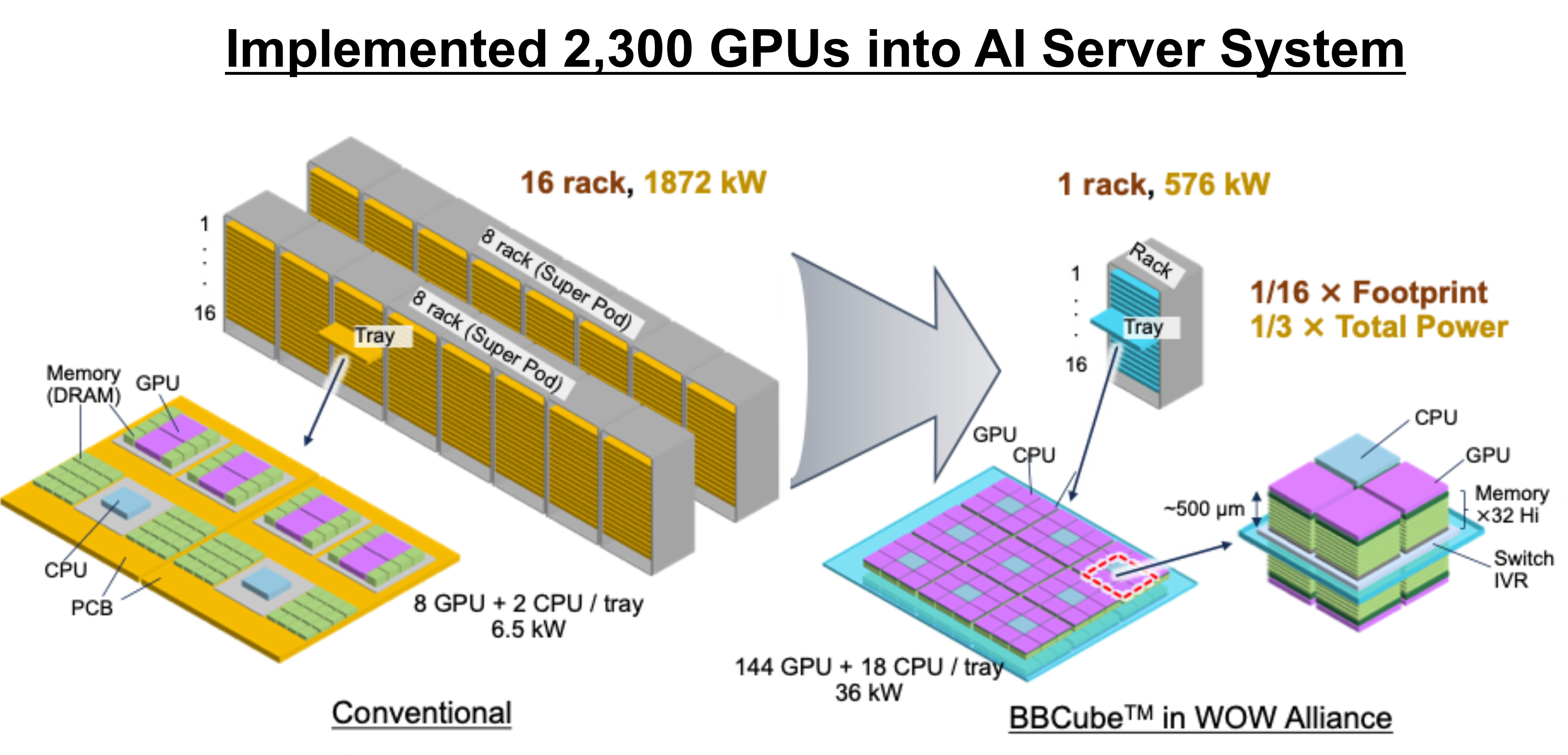

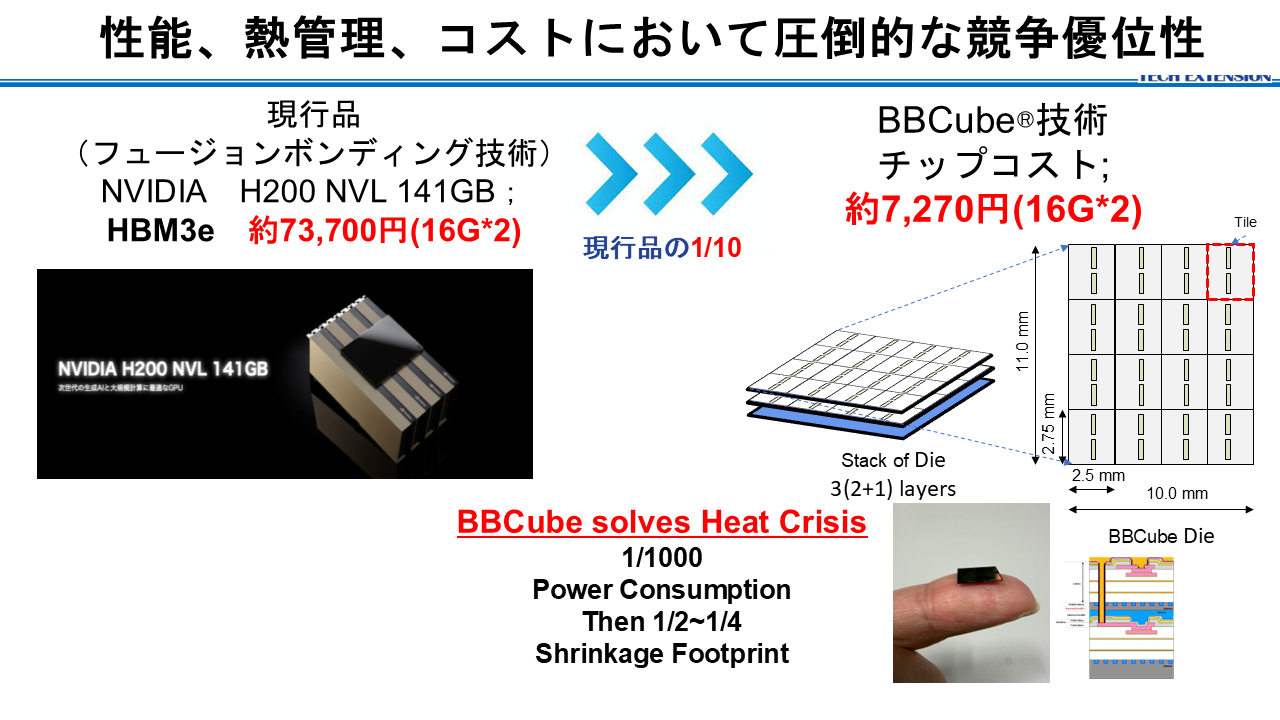

BBCubeが実現する構造的革新による、10×〜1000×の圧倒的な効率向上

BBCubeはシステム効率を劇的に引き上げ、従来の構造的制約を打破する以下の「5つの付加価値」を実現します。

◆ インターコネクトの電力消費を最大1/1000まで削減

◆ 発熱を約50%削減

◆ システムのフットプリントを1/2〜1/4に縮小

◆ 圧倒的な低インピーダンス接続を実現

◆ AIシステム向けの大規模並列I/Oの実現

AIハードウェアにおける経済構造の変革

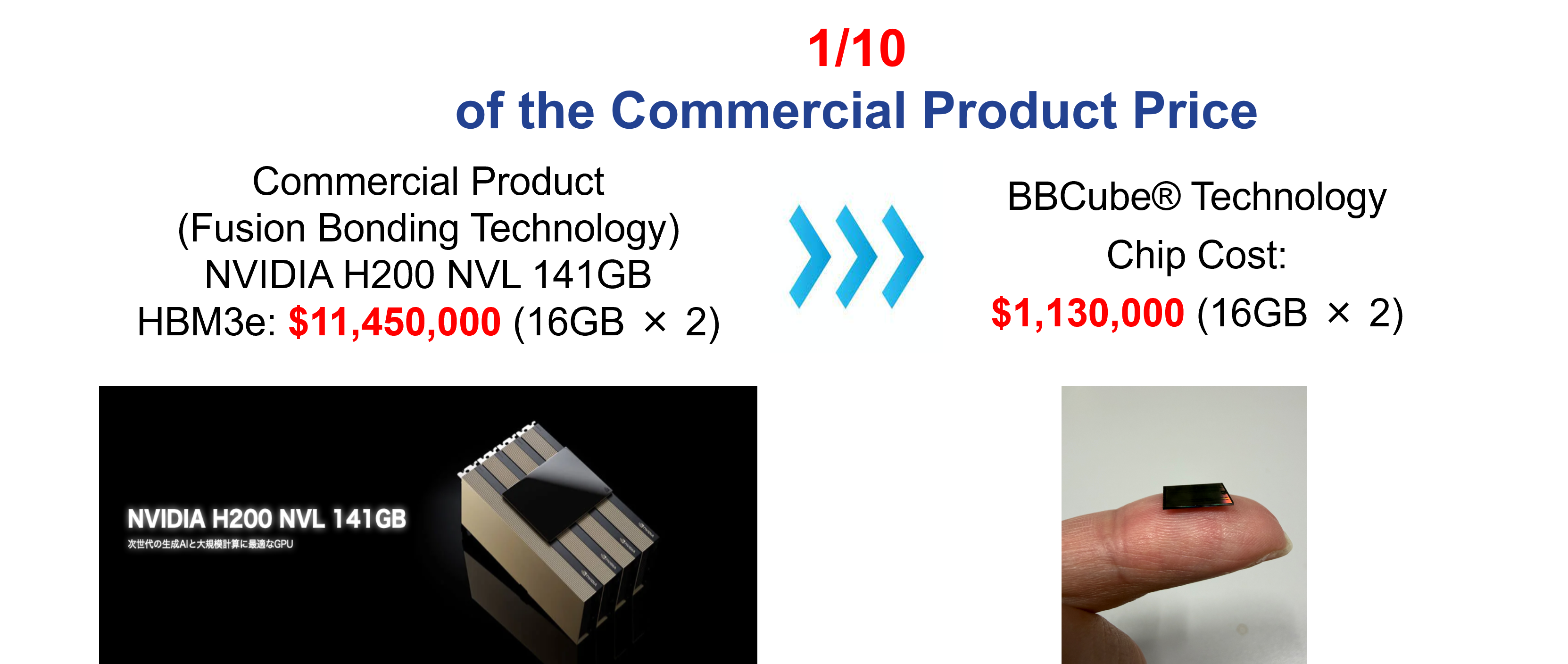

BBCubeは、次世代AIハードウェアの経済構造を根本から再定義します。

◆ 同等ソリューション比でチップコストを約1/10まで削減できる可能性

◆ ラック密度の向上

◆ 冷却インフラコストの低減

◆ ハイパースケールAI導入における、より優れた電力効率(Performanceper-Watt)の実現

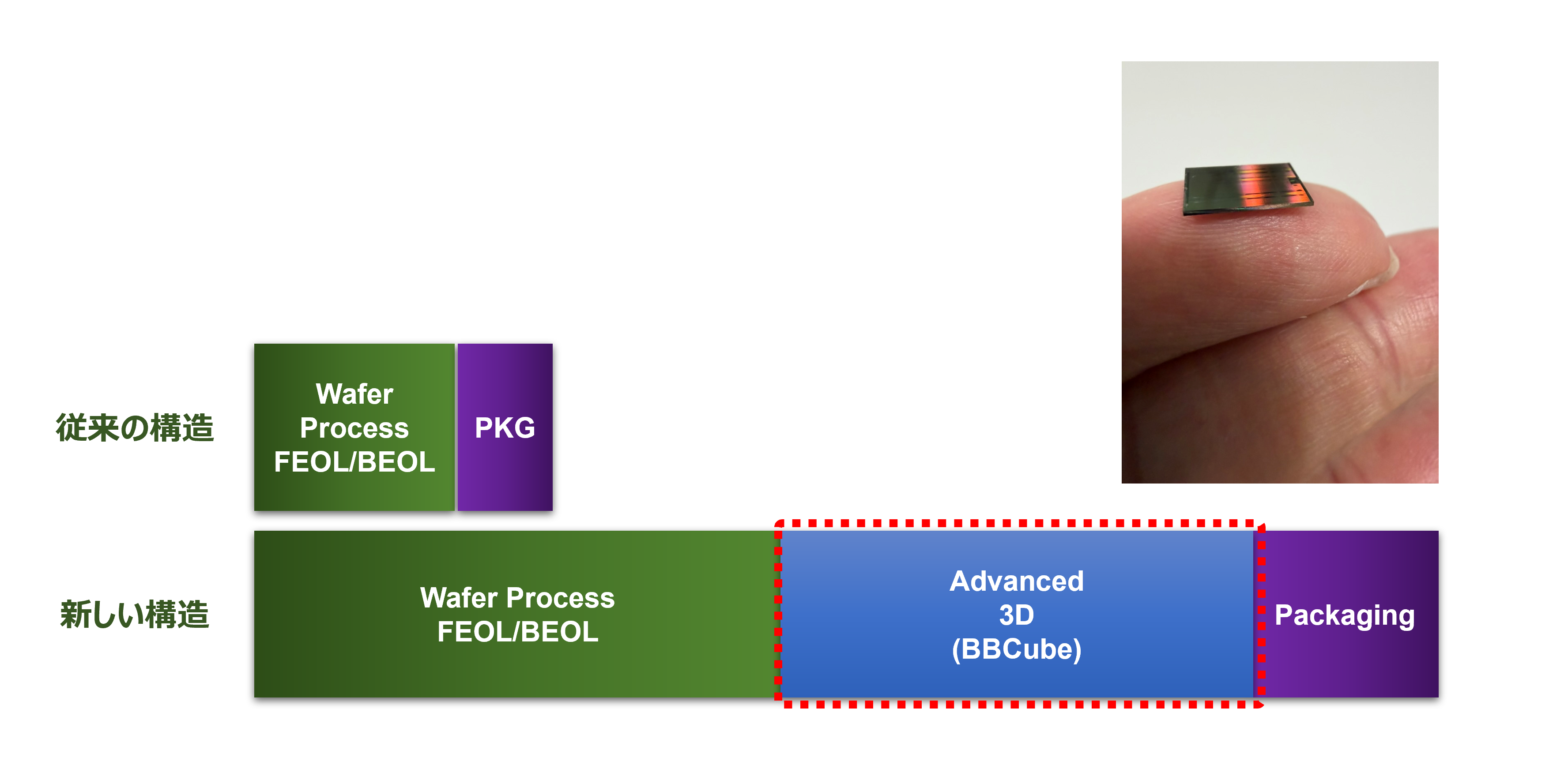

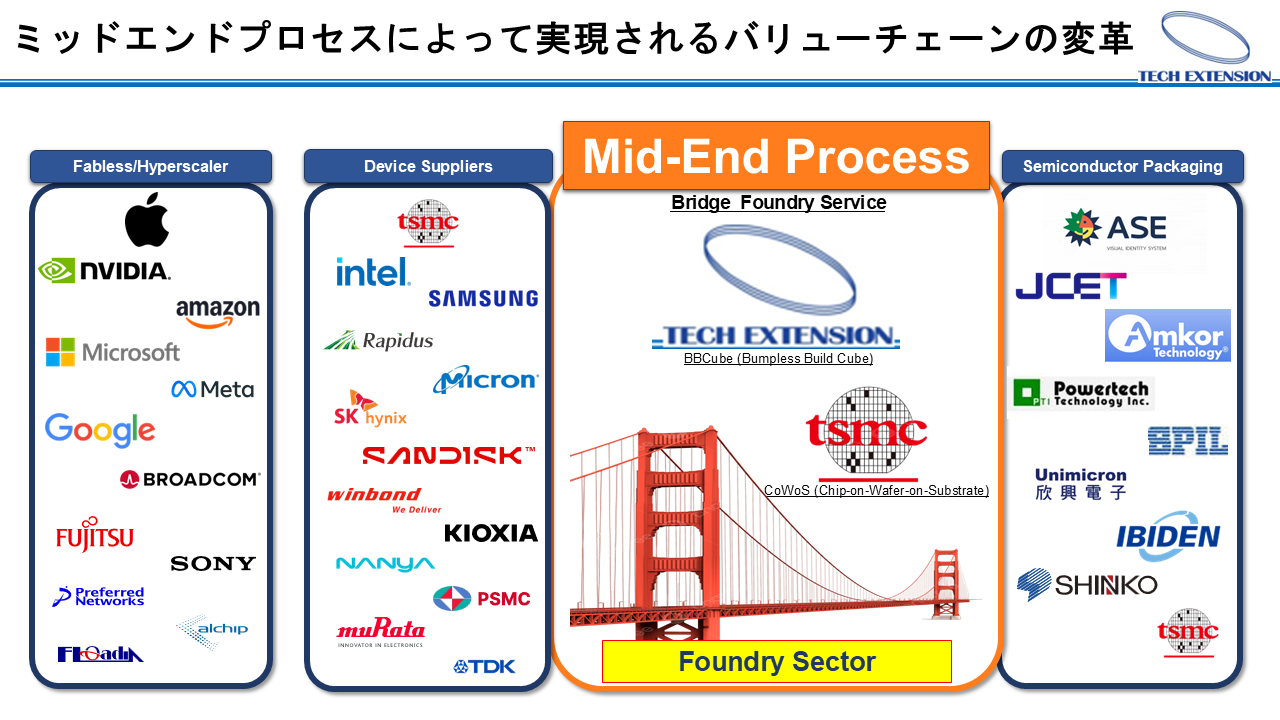

新たな産業レイヤー : ミッドエンド統合プラットフォーム

刻々と進化する半導体の技術スタックにおいて、BBCubeは新たな産業レイヤーとして

異種AIチップ向けのスケーラブルなミッドエンド統合プラットフォーム を導入します。

【従来の構造】:FEOL → BEOL → パッケージング

【新しい構造】:FEOL → BEOL → ミッドエンド3Dインテグレーション → パッケージング

その他技術紹介

用語解説(Glossary)

| WOWアライアンス | 東京科学大学科学技術創成研究院異種機能集積研究ユニット(大場研究室)における産学研究プラットフォーム。 半導体関連の設計・プロセス・装置・材料などを手がける企業、および研究機関によって構成される。三次元開発としては国内唯一300ミリウエハを利用した実証開発、高度かつ簡便なウエハの薄化技術・積層技術を持ち、バンプ(注6)レスTSV配線を用いた三次元化技術を世界で初めて開発に成功した。 |

| 台湾国立成功大学 | 1931年に創設された国立総合大学であり、台湾中南部で最難関大学として知られ、指定国立研究大学6校の一つである。 英語: National Cheng Kung University (NCKU)、公用語表記: 國立成功大學。(Wikipediaより引用) |

| BBCube | Bumpless Build Cubeの略で、従来の平置きチップレットを三次元でコンパクトにまとめ、バンプを利用しないでシステムの小型化を可能にするアーキテクチャー。 参考:Ohba, T.; Sakui, K.; Sugatani, S.; Ryoson, H.; Chujo, N. Review of Bumpless Build Cube (BBCube) Using Wafer-on-Wafer (WOW) and Chip-on-Wafer (COW) for Tera-Scale Three-Dimensional Integration (3DI). Electronics 2022, 11, 236. https://doi.org/10.3390/electronics11020236 |

| 次世代三次元集積技術 | ウエハレベルで三次元集積を行う次世代半導体技術。 WOWアライアンスが保有する超薄化技術、バンプを除いた垂直配線技術で半導体の三次元集積を行い、従来よりも高性能・低消費電力を実現することができる。またサーバーなどの大規模演算デバイスだけでなく、搭載される異種機能デバイスシステムの超小型化が可能になる。 |

| WOW技術 | Wafer-on-Wafer技術の略で、ウエハ上にウエハを接合しながら接続配線し、何枚も積み上げることができる積層技術。 DRAMなど同一チップサイズのウエハ積層の生産性向上に大きく寄与します。 |

| COW技術 | Chip-on-Wafer技術の略で、チップレットをウエハ上に接合しながらWOW技術で接続配線する技術。 チップをウエハ上に接合することにより、以降の半導体製造工程において、各種ウエハプロセス装置を用いた高精度な加工が行えるようになる。 |

| HBM | High Bandwidth Memoryの略。 JEDECが規格化した、Through Silicon Via (TSV)技術によるダイスタッキングを前提としたメモリ規格である。(Wikipediaより引用) |

| DDR5 | DDR5 SDRAM (Double Data Rate 5 Synchronous Dynamic Random-Access Memory)の略。 半導体集積回路で構成されるDRAMの規格の一種であり、複数のDRAMチップをプリント基板上に搭載したメモリモジュール(DIMM = Dual Inline Memory Module)として、コンピュータの主記憶として利用される。前世代のDDR4 SDRAMと比較して、DDR5は消費電力を削減しつつ帯域幅が2倍になる。(Wikipediaより引用) |

| TSV | Through-Silicon-Viaの略で、シリコン(Silicon)ウエハを貫通(Through)させて開けた接続孔(Via:ビア)。 上下に積層したチップを、埋め込み配線によって接続させる。最近では、シリコン材料以外にも配線するため、前工程における垂直配線(vertical interconnects)とした方が分かりやすい。 |